什么是 EMC 整改?

EMC整改是指电子电气产品在电磁兼容(EMC)测试中,因电磁干扰(EMI)超标或抗扰度(EMS)不足不符合标准时通过技术调整(如电路优化、屏蔽、滤波等)使产品达到合规要求的过程。核心是定位问题根源(干扰源、干扰路径、敏感部件),采取针对性措施,确保产品在电磁环境中既能正常工作,又不对其他设备造成干扰。

辐射干扰(RE)整改分享

辐射干扰(RE,Radiated Emission)测试是 EMC 干扰测试的重要项目,用于评估产品通过空间向外发射的电磁波是否在标准允许范围内,避免对周围设备(如无线电、通信设备、医疗仪器等)造成干扰。若产品在 RE 测试中出现辐射超标,需进行以下整改:

1.RE 干扰的特点

干扰以电磁波形式通过空间传播,频率范围通常为 30MHz~1GHz(或更高),主要由产品内部的高频电路(如时钟电路、射频模块)、快速开关信号(如 PWM 信号)、线缆或 PCB 布线作为 “发射天线” 产生。

2.常见问题原因

高频干扰源未抑制:如微处理器的时钟信号、电源模块的开关频率、射频电路的杂散发射等,自身产生的高频信号通过空间辐射;

线缆成为发射天线:内部连接线(如电源线、信号线、排线)未屏蔽或布线混乱,将电路中的高频干扰信号耦合后向外辐射;

PCB 设计缺陷:高频信号线过长、布线不合理(如形成大环路)、接地不良(如接地平面不完整、多点接地导致干扰耦合),导致信号辐射增强;

壳体屏蔽不良:产品外壳缝隙过大、未接地或屏蔽材料不佳,内部辐射信号通过壳体泄露。

3.整改措施

抑制干扰源:

降低高频信号的辐射强度:如降低时钟电路的频率(在功能允许范围内)、优化 PWM 信号的上升/下降时间(增加缓动电路),减少高频谐波;

对干扰源电路加滤波:在时钟芯片、射频模块的电源引脚处增加高频滤波电容(如 0.1μF 陶瓷电容),或串联磁珠,抑制干扰信号传导;

隔离强干扰电路:将电源模块、电机驱动等强干扰电路与其他电路物理隔离,避免干扰扩散;

处理发射天线(线缆与 PCB):

缩短高频信号线长度,避免形成长导线“天线”;

增加完整接地平面(GND 层),将高频信号线靠近接地平面,利用接地平面吸收辐射减少 PCB 上的信号环路面积(如差分线配对布线、电源线与地线并行),降低环路辐射;

线缆屏蔽与接地:对外部连接的电源线、信号线采用屏蔽线缆,屏蔽层单端或两端接地(低频单端接地,高频两端接地),减少线缆的辐射能力;

优化 PCB 布线:

增强壳体屏蔽:

密封壳体缝隙:对产品外壳的缝隙、通风孔加装导电屏蔽材料(如导电泡棉、铜网),确保缝隙处导电连接,减少辐射池露;壳体接地:将金属外壳与设备接地平面可靠连接,通过接地吸收内部辐射信号。

整改验证

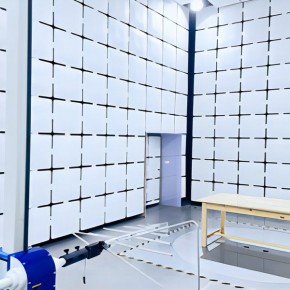

整改后需重新进行 RE 测试,验证产品在各频率点的辐射发射值是否低于标准限值(如 CE 认证的 EN 301489 系列、FCC认证的 Part 15 等),直至达标。

通过 RE 整改,可有效降低产品的电磁辐射水平,确保其不对周围设备造成干扰,满足市场准入的 EMC 合规要求.